|

来源:半导体芯闻

张晓强强调,这是他投入半导体领域20多年来最令他感到兴奋的时候,正如另一副共同营运长侯永清指出,半导体黄金时刻已到来,而未来AI芯片发展,接近99%将靠台积电先进逻辑技术和先进封装支持,而台积电技术创新,已可看到未来在技术持续推进下,发挥芯片更高的效能及更优异能耗表现。 他表示,台积电在2纳米基础下,全球首创的A16纳米制程技术,搭配独家开发的超级电轨(即晶背供电)技术,让产出的芯片在相同速度下效能比2纳米再高出8~10%,在相同面积下,节耗减少15%到20%,台积电已计划在2026年导入量产,首颗芯片将用于资料中心高效能运算(HPC)芯片。 此外,台积电也成功在实验证整合P-FET和N-FET二种不同型态晶体管,做出CFET架构的芯片,这是2纳米采用纳米片(Nano Sheet)架构创新后,下一个全新晶体管架构创新。 张晓强并对与会的开发工程师表示,继CFET后,台积电研发人员也持续寻求更多整合更多晶体管新材料和创新架构,比如Ws2或WoS2等无机纳米管或纳米碳管(carbon nanotube) ,意谓台积电可预见未来将CFET导入更先进埃米级制程外,也会持续推动更先进晶体管架构创新。 台积电业务开发、海外营运资深副总暨副共同营运长张晓强指出,台积电最新的A16 制程不一定会使用High NA EUV,在哪一代使用还不确定,但之后会再针对成本、利润进行评估。 至于「系统级晶圆」(System on Wafer,SoW)这项技术,张晓强表示最重要是客户可以把更多HBM 结合在一起,把几十个HBM 和Logic Die(裸晶)整合,对未来数据频宽(Data Bandwidth)、高效能运算有重要提升,尤其是AI 会有很多应用。

在被问到与SK 海力士的合作关系,张晓强表示与所有HBM 供应商都有合作,主要看客户选择SK 海力士、三星和美光哪间公司,而台积电与三间供应商都有深厚的合作关系。SK 海力士是HBM 领头羊,走在前面,要将逻辑芯片和HBM 整合起来需要很多先进技术,当中也会遇到许多问题需要一起解决。 最后针对硅光子问题,张晓强预期硅光子会先导入资料中心,因为需要高效能,在制程部分主要分为两种,有些部分65 纳米以上成熟制程即可采用,另一个部分是电和光的转换,因为电的速度越来越快,需要先进制程7 纳米甚至5 纳米加入。

不过,张晓强表示,未来推动AI芯片效能持续精进,除了靠台积电的逻辑制程持续推动和创新外,也要搭配先进封装架构。他今日秀出台积电扩大整合涵盖记忆体、后段封装和基板所建构3D IC平台,整合iC设计IP、制造到后段封测整体解决方案,提供不同AI需求芯片整合服务,还包括导入更高效输出的硅光子元件封装(CPO),让半导体产业进入另一新的里程碑。 今年盖七个厂3纳米扩充产能仍不够使用

台积电负责3纳米量产的厂长资深厂长18B厂长黄远国23日首度在台积技术论坛台湾场次主讲卓越制造议题,他说,台积先进制程3纳米去年开始量产同时期和N4良率一样,3纳米扩充产能仍不够使用,今年台积整体将盖七个厂包含台湾三个晶圆厂两个封装厂与海外两个厂都在进行。

台积电卓越制造议题一向是业界焦点,过往先后由「秦工」总工程师执行副总经理暨共同营运长秦永沛、王英郎(营运/ 晶圆厂营运一副总经理)、张宗生台积科技院士、营运/ 先进技术暨光罩工程副总经理主讲,此次则首度由最先进制程关键推手、厂长级主管在台湾场次登台演讲。

他提到,统计2024年台积电特殊制程在成熟比重也稳定成长,从2020的61%在2024年目标达到67%,2022-2023年平均盖五个厂,至于今年盖七个厂是包含三个晶圆厂两个封装厂以及海外两个厂都在进行。

台湾厂方面,他提到,新竹与高雄为2纳米量产基地,进展顺利已陆续进机,台中AP5为了CoWos扩产所需,近期宣布的嘉义先进封装投资则为CoWos与SOIC生产。

他也说,美国厂晶圆21厂预定明年量产,并预定二厂2028年量产。熊本晶圆23厂以外第二场预定2027年量产,德国厂预定今年第四季动工目前在忙碌准备预定2027年量产,南京厂也正稳定扩充28纳米产能,相关布局都是为了满足与支持客户所需。

谈到EUV应用,他提到,台积2019年迄今机台数已成长十倍且占全球65%,晶圆产出量与效率皆随着学习大幅提升。

他说,台积全球制造与管理平台实现One Fab概念,能让台积横跨全球的晶圆厂达到一定效率并在全球厂区投入绿色制造人才培养、供应链在地化。

台积电最新路线图

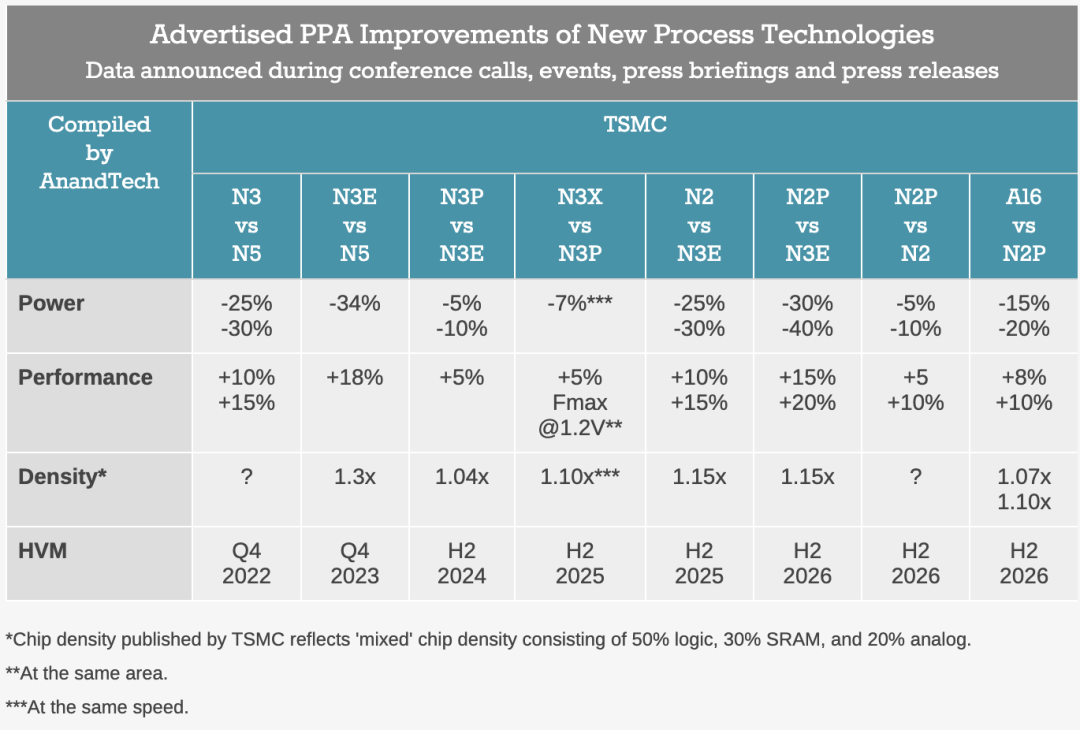

正如台积电上周宣布的,该公司将于今年晚些时候开始采用 N3P 制造工艺进行大批量生产,这将是该公司一段时间内最先进的节点。明年事情会变得更有趣,因为台积电将拥有两种工艺技术,当它们在 2025 年下半年进入大批量制造 (HVM) 时,它们实际上可以相互竞争。

台积电的 N2 将是台积电首个采用全栅 (GAA) 纳米片晶体管的生产节点,这将显著提升其性能、功率和面积 (PPA) 特性。与 N3E 相比,在 N3 上生产的半导体可将其功耗降低 25% - 30%(在相同的晶体管数量和频率下),将其性能提高 10% - 15%(在相同的晶体管数量和功率下),并将晶体管密度提高 15%(在相同的速度和功率下)。

虽然 N2 在功耗和晶体管密度方面肯定是台积电无可争议的冠军,但在性能方面,N3X 可能会挑战它,尤其是在高电压下。对于许多客户来说,N3X 还将受益于使用经过验证的 FinFET 晶体管,因此 N2 在 2025 年下半年不会自动成为台积电的最佳节点。

明年,台积电将再次提供两个针对普遍相似的智能手机和高性能计算应用的节点:N2P(性能增强的 2 纳米级)和 A16(具有背面供电的 1.6 纳米级)。

与最初的 N2 相比,N2P 的功耗有望降低 5% - 10%(在相同的速度和晶体管数量下),性能有望提高 5% - 10%(在相同的功耗和晶体管数量下)。与此同时,与 N2P 相比,A16 的功耗有望降低高达 20%(在相同的速度和晶体管数量下),性能有望提高高达 10%(在相同的功耗和晶体管数量下),晶体管密度有望提高高达 10%。

请记住,A16 具有增强的背面供电网络,因此它很可能成为注重性能的芯片设计师的首选节点。但当然,使用 A16 会更昂贵,因为背面供电需要额外的工艺步骤。 *声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。 |

版权所有 本站内容未经书面许可,禁止一切形式的转载。© Copyright 2017 无锡卓海科技股份有限公司 版权所有. All rights reserved. | 苏ICP备10225498号 |

建议您使用IE8.0及以上版本浏览器登陆本站点。